In digital electronics, an address decoder is a binary decoder that has two or more inputs for address bits and one or more outputs for device selection signals.[1] When the address for a particular device appears on the address inputs, the decoder asserts the selection output for that device. A dedicated, single-output address decoder may be incorporated into each device on an address bus, or a single address decoder may serve multiple devices.[2]

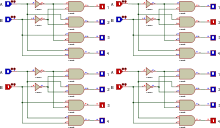

A single address decoder with n address input bits can serve up to 2n devices. Several members of the 7400 series of integrated circuits can be used as address decoders. For example, when used as an address decoder, the 74154[3] provides four address inputs and sixteen (i.e., 24) device selector outputs. An address decoder is a particular use of a binary decoder circuit known as a "demultiplexer" or "demux" (the 74154 is commonly called a "4-to-16 demultiplexer"), which has many other uses besides address decoding.

Address decoders are fundamental building blocks for systems that use buses. They are represented in all integrated circuit families and processes and in all standard FPGA and ASIC libraries. They are discussed in introductory textbooks in digital logic design.[1]

YouTube Encyclopedic

-

1/3Views:30 7412 024 80128 599

-

Dynamic Random Access Memory (DRAM). Part 3: Binary Decoders

-

Introduction to Encoders and Decoders

-

Address Decoding And Reading From Memory

Transcription

Address decoder selects the storage cell in a memory

An address decoder is a commonly used component in microelectronics that is used to select memory cells in randomly addressable memory devices.

Such a memory cell consists of a fixed number of memory elements or bits. The address decoder is connected to an address bus and reads the address created there. Using a special switching logic, it uses this address to calculate which memory cell is to be accessed. It then selects that cell by selecting it via a special control line. This line is also known as the select line. In dynamic memories (DRAM), there are row and column select lines on the memory matrix, which are controlled by address decoders integrated in the chip.

Depending on the type of decoder, the logic used to select the memory cell can under certain circumstances be programmable.

Address decoder selects the appropriate memory module

An address decoder is also used to select the appropriate one of multiple memory modules or memory chips when a particular address is provided by the processor system's address bus.

For this purpose, the memory modules or memory chips have selection inputs, usually referred to as chip select pin (CS) or chip enable pin (CE) pin. These inputs often have a negative logic function (CS or CE), i. H. with an adjacent logical zero (voltage level low) is selected.

The address decoder uses the different combinatorial logic to place the memory modules or chips in the address space of a processor. The memory modules often have a smaller capacity than the address space. In most cases, several modules can be used, even if they are completely identical in structure. It must be ensured that they differ in the address range.

References

- ^ a b Paul Horowitz and Winfield Hill (1989). The Art of Electronics (2nd ed.). Cambridge University Press. p. 685,766. ISBN 978-0-521-37095-0.

- ^ S. J. Cahill (1993). Digital and microprocessor engineering (2nd ed.). Ellis Horwood. pp. 489–494. ISBN 978-0-13-213398-2.

- ^ Datasheet for 74HCT154